隨著高性能嵌入式系統(tǒng)在通信、雷達(dá)、工業(yè)控制等領(lǐng)域的快速發(fā)展,對(duì)設(shè)備間高速、可靠、低延遲的互連通信需求日益迫切。RapidIO作為一種高性能、低引腳數(shù)、基于包交換的互連架構(gòu),特別適用于芯片間和板卡間的通信。而數(shù)字信號(hào)處理器(DSP)憑借其強(qiáng)大的實(shí)時(shí)信號(hào)處理能力,成為許多計(jì)算密集型系統(tǒng)的核心。將兩者結(jié)合,構(gòu)建基于DSP的RapidIO通信系統(tǒng),能夠顯著提升系統(tǒng)的整體性能和靈活性。本文旨在探討該系統(tǒng)的軟硬件設(shè)計(jì)關(guān)鍵,并介紹相關(guān)的技術(shù)咨詢與集成服務(wù)。

一、系統(tǒng)硬件設(shè)計(jì)關(guān)鍵

硬件設(shè)計(jì)是系統(tǒng)穩(wěn)定運(yùn)行的基石,主要涉及以下幾個(gè)核心方面:

- DSP選型與RapidIO接口:選擇支持RapidIO互連(通常為SRIO,Serial RapidIO)的DSP芯片是首要步驟。需根據(jù)處理性能、接口數(shù)量(1x/4x)、傳輸速率(如1.25Gbaud, 2.5Gbaud, 3.125Gbaud per lane)以及功耗、成本進(jìn)行綜合評(píng)估。主流廠商如TI的C6000系列、ADI的SHARC系列等均提供了豐富的選擇。

- 物理層與電路設(shè)計(jì):RapidIO物理層采用串行差分信號(hào)(LVDS),對(duì)PCB布局布線有嚴(yán)格要求。需要精心設(shè)計(jì)高速信號(hào)線的阻抗控制、等長(zhǎng)匹配、層疊結(jié)構(gòu),并處理好電源完整性與信號(hào)完整性,以確保信號(hào)質(zhì)量,減少誤碼。

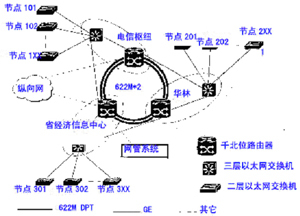

- 系統(tǒng)架構(gòu)與拓?fù)?/strong>:根據(jù)應(yīng)用需求確定系統(tǒng)拓?fù)浣Y(jié)構(gòu),如星型、環(huán)型或網(wǎng)狀。設(shè)計(jì)背板或板間連接方案,可能涉及RapidIO交換芯片(Switch)的使用,以實(shí)現(xiàn)多DSP節(jié)點(diǎn)或多個(gè)設(shè)備(如FPGA、CPU)之間的互連與數(shù)據(jù)交換。

- 輔助電路與電源管理:設(shè)計(jì)可靠的時(shí)鐘電路、復(fù)位電路、配置電路(如EEPROM存儲(chǔ)設(shè)備ID)以及滿足DSP和RapidIO接口需求的電源軌與時(shí)序管理。

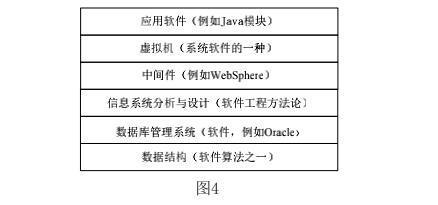

二、系統(tǒng)軟件設(shè)計(jì)關(guān)鍵

軟件負(fù)責(zé)驅(qū)動(dòng)硬件并實(shí)現(xiàn)高效的數(shù)據(jù)傳輸與控制,是發(fā)揮系統(tǒng)效能的關(guān)鍵。

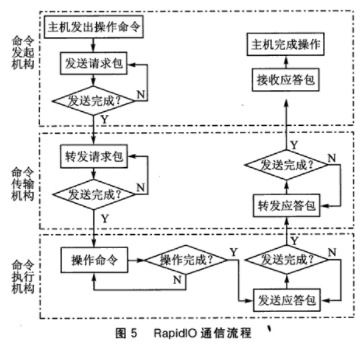

- 底層驅(qū)動(dòng)開發(fā):開發(fā)或移植DSP側(cè)與RapidIO控制器(SRIO外設(shè))相關(guān)的底層驅(qū)動(dòng)程序。這包括初始化配置(設(shè)置設(shè)備ID、速率、端口寬度)、維護(hù)鏈路狀態(tài)、處理錯(cuò)誤中斷等。通常需要深入理解芯片手冊(cè)和RapidIO協(xié)議。

- 數(shù)據(jù)傳輸模型編程:RapidIO支持直接IO(DIO)和消息傳遞(Message Passing)兩種主要數(shù)據(jù)傳輸模型。需要根據(jù)應(yīng)用場(chǎng)景(如大數(shù)據(jù)流傳輸或小規(guī)模控制消息)選擇合適的模型,并編寫相應(yīng)的數(shù)據(jù)發(fā)送/接收、門鈴(Doorbell)中斷處理、數(shù)據(jù)包(Packet)組裝與解析代碼。

- 操作系統(tǒng)集成與優(yōu)化:若系統(tǒng)運(yùn)行在SYS/BIOS(TI)或其他實(shí)時(shí)操作系統(tǒng)上,需要將RapidIO通信機(jī)制與任務(wù)調(diào)度、內(nèi)存管理、中斷服務(wù)等模塊無(wú)縫集成。優(yōu)化數(shù)據(jù)緩沖策略(如使用EDMA進(jìn)行高效搬移)以減少CPU開銷和傳輸延遲。

- 高層應(yīng)用協(xié)議與API:在底層驅(qū)動(dòng)之上,可以封裝更易用的應(yīng)用編程接口,甚至實(shí)現(xiàn)特定的高層通信協(xié)議(如自定義的可靠傳輸協(xié)議、數(shù)據(jù)分發(fā)協(xié)議),以簡(jiǎn)化上層應(yīng)用程序的開發(fā)。

三、設(shè)計(jì)挑戰(zhàn)與應(yīng)對(duì)策略

- 挑戰(zhàn)一:高速信號(hào)完整性。應(yīng)對(duì):借助仿真工具進(jìn)行前仿真與后仿真,嚴(yán)格遵守高速設(shè)計(jì)規(guī)則,必要時(shí)進(jìn)行硬件測(cè)試與調(diào)試。

- 挑戰(zhàn)二:復(fù)雜協(xié)議與調(diào)試?yán)щy。應(yīng)對(duì):利用芯片廠商的分析工具(如TI的RapidIO Navigator Analyzer)和邏輯分析儀進(jìn)行數(shù)據(jù)包抓取與分析,采用分模塊、增量式的開發(fā)與測(cè)試方法。

- 挑戰(zhàn)三:系統(tǒng)性能優(yōu)化。應(yīng)對(duì):通過分析瓶頸(是DSP處理速度、DMA帶寬還是鏈路速率),針對(duì)性優(yōu)化代碼、調(diào)整緩沖區(qū)大小、優(yōu)化傳輸模式(如流控窗口)。

四、技術(shù)咨詢與集成服務(wù)

針對(duì)企業(yè)在開發(fā)此類系統(tǒng)時(shí)可能面臨的技術(shù)門檻高、周期長(zhǎng)、經(jīng)驗(yàn)不足等問題,專業(yè)的咨詢與技術(shù)服務(wù)至關(guān)重要。我們可提供以下支持:

- 方案咨詢與評(píng)估:根據(jù)客戶的具體應(yīng)用場(chǎng)景(如雷達(dá)數(shù)據(jù)交換、無(wú)線基站基帶池、醫(yī)療成像)、性能指標(biāo)和成本預(yù)算,提供最優(yōu)的DSP選型、RapidIO拓?fù)浼罢w架構(gòu)設(shè)計(jì)建議。

- 硬件設(shè)計(jì)服務(wù):提供從原理圖設(shè)計(jì)、PCB Layout(重點(diǎn)關(guān)注高速信號(hào)部分)到硬件調(diào)試、信號(hào)測(cè)試的全流程或關(guān)鍵環(huán)節(jié)支持服務(wù)。

- 軟件設(shè)計(jì)與開發(fā):提供底層SRIO驅(qū)動(dòng)開發(fā)、數(shù)據(jù)傳輸模塊開發(fā)、操作系統(tǒng)移植與優(yōu)化,以及定制化應(yīng)用協(xié)議開發(fā)等服務(wù)。

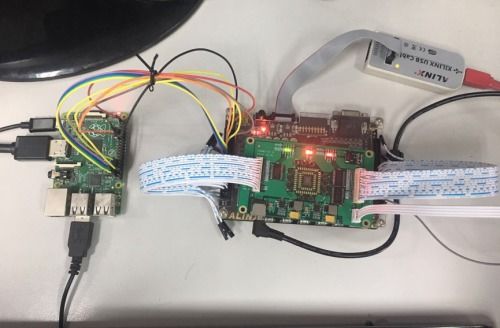

- 系統(tǒng)集成與測(cè)試:協(xié)助客戶將軟硬件模塊進(jìn)行集成,完成系統(tǒng)級(jí)聯(lián)調(diào),進(jìn)行壓力測(cè)試、穩(wěn)定性測(cè)試和性能基準(zhǔn)測(cè)試,確保系統(tǒng)達(dá)到設(shè)計(jì)目標(biāo)。

- 技術(shù)培訓(xùn)與支持:提供RapidIO協(xié)議、DSP編程及系統(tǒng)調(diào)試相關(guān)的技術(shù)培訓(xùn),并在項(xiàng)目全周期提供持續(xù)的技術(shù)支持與問題解答。

###

基于數(shù)字信號(hào)處理器的RapidIO通信系統(tǒng)設(shè)計(jì)是一項(xiàng)涉及多學(xué)科知識(shí)的復(fù)雜工程。成功的實(shí)現(xiàn)不僅依賴于扎實(shí)的硬件設(shè)計(jì)能力和深入的軟件編程技巧,更離不開對(duì)RapidIO協(xié)議與DSP架構(gòu)的透徹理解。通過借助專業(yè)的技術(shù)咨詢與集成服務(wù),客戶可以有效降低開發(fā)風(fēng)險(xiǎn)、縮短產(chǎn)品上市時(shí)間,從而更專注于自身核心算法的實(shí)現(xiàn)與創(chuàng)新,最終在激烈的市場(chǎng)競(jìng)爭(zhēng)中占據(jù)先機(jī)。